### **Center-Wide Procedures and Guidelines (PG)**

| DIRECTIVE NO.    | 500-PG-8700.2.7B | APPROV | ED BY Signature: | Original Signed By |

|------------------|------------------|--------|------------------|--------------------|

| EFFECTIVE DATE:  | August 13, 2012  | NAME:  | Felicia Jones    |                    |

| EXPIRATION DATE: | March 30, 2021   | TITLE: | Director, AETD   |                    |

#### **COMPLIANCE IS MANDATORY**

**Responsible Office:** 500/Applied Engineering and Technology Directorate

Title: Design of Space Flight Field Programmable Gate Arrays

### TABLE OF CONTENTS

| 1   | SPECIAL PINS                                       | 7   |

|-----|----------------------------------------------------|-----|

| 1.1 | CONFIGURATION PINS                                 | . 7 |

| 1.2 | UNUSED INPUTS                                      |     |

| 1.3 | TEST INTERFACE                                     | 8   |

| 1.4 | DEBUG INTERFACE                                    | 8   |

| 2   | INPUT/OUTPUT (I/O)                                 | 8   |

| 2.1 | SIMULTANEOUS SWITCHING OUTPUTS (SSOS)              | . 8 |

| 2.2 | SIGNAL TERMINATION                                 | 10  |

| 2.3 | TRI-STATE BUS CONSIDERATIONS                       |     |

| 2.4 | INPUT TRANSITION TIMES                             |     |

| 2.5 | SHORTING OUTPUTS TOGETHER                          |     |

| 2.6 | MIXED I/O STANDARDS                                |     |

| 2.7 | Power Switching and Cold Sparing                   | 13  |

| 3   | CLOCKS                                             | 15  |

| 3.1 | CLOCK BUFFERS                                      | 15  |

| 3.2 | CHIP-TO-CHIP TIMING STRATEGY                       |     |

| 3.3 | DELAY LOCK LOOPS, DLLS, AND PHASE LOCK LOOPS, PLLS |     |

| 3.4 | CLOCK TREE DIAGRAM                                 |     |

| 3.5 | CROSSING CLOCK DOMAINS                             |     |

| 3.6 | FLIP-FLOP REPLICATION                              |     |

| 3.7 | OPPOSITE EDGE CLOCKING                             |     |

| 3.8 | METASTABILITY                                      |     |

| 3.9 | LATCHES                                            |     |

| 4   | FINITE STATE MACHINES, FSM                         |     |

| 4.1 | CRITICAL STATE MACHINES                            |     |

| 4.2 | STATE ENCODING                                     |     |

| 4.3 | HDL SYNTHESIZED MACHINES                           |     |

| 4.4 | ERROR DETECTION AND CORRECTION, EDAC               |     |

| 5   | RESET                                              | 21  |

| 5.1 | RESET LOGIC CIRCUIT (CONSIDER TRANSIENT BEHAVIOR)  |     |

| 5.2 | Resets                                             | 22  |

| 5.3 | Reset Tree                                         |     |

| 5.4 | COMPONENT STARTUP TIME                             |     |

| 5.5 | MISSION CRITICAL SIGNALS                           | 23  |

| 6   | HAZARD ANALYSIS                                    | 24  |

|     | CHECK THE GSFC DIRECTIVES MANAGEMENT SYSTEM AT     |     |

http://gdms.gsfc.nasa.gov to verify that this is the correct version prior to use.

DIRECTIVE NO.

500-PG-8700.2.7B

EFFECTIVE DATE:

August 13, 2012

EXPIRATION DATE:

March 30, 2021

| 6.1                                                                                                                                                    | STATIC HAZARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2                                                                                                                                                    | DYNAMIC HAZARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                              |

| 7                                                                                                                                                      | POWER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

| 7.1                                                                                                                                                    | SUPPLY SEQUENCING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |

| 7.2<br>7.3                                                                                                                                             | SIGNALS INTO UNPOWERED CMOS I/O'S<br>Startup Voltage Rise Time                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                              |

| 7.4                                                                                                                                                    | BYPASSING AND DISTRIBUTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                              |

| 8                                                                                                                                                      | INTERFACING TO NON-VOLATILE MEMORIES (EEPROM, FLASH, ETC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              |

| 8.1                                                                                                                                                    | PROTECTION DURING POWER-UP/DOWN TRANSITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

| 8.2                                                                                                                                                    | ANALYSIS OF DAMAGE DURING WRITE CYCLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                              |

| 8.3<br>8.4                                                                                                                                             | CYCLE COUNT<br>TRANSIENTS AND NOISE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                              |

| 8.5                                                                                                                                                    | RELIABILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

| 8.6                                                                                                                                                    | Refreshing and Reloading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| 8.7                                                                                                                                                    | RECOMMENDATIONS AND TIPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| 9                                                                                                                                                      | TIMING ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                              |

| 9.1                                                                                                                                                    | Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                              |

| 9.2                                                                                                                                                    | FLIP FLOPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                              |

| 9.3                                                                                                                                                    | Environmental Effects<br>Speed Grade                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |

| 9.4<br>9.5                                                                                                                                             | SPEED GRADE<br>Asynchronous Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                              |

| 9.6                                                                                                                                                    | TIMING MARGIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                              |

|                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                              |

| 10                                                                                                                                                     | MISCELLANEOUS DESIGN GUIDELINES AND CRITERIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                              |

| 10.1                                                                                                                                                   | Noise Immunity and Quiet Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

| 10.1<br>10.2                                                                                                                                           | Noise Immunity and Quiet Designs<br>Defensive Design and Designing for Off-Nominal Events                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              |

| 10.1<br>10.2<br>10.3                                                                                                                                   | Noise Immunity and Quiet Designs<br>Defensive Design and Designing for Off-Nominal Events<br>Designing For Testability                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                              |

| 10.1<br>10.2                                                                                                                                           | Noise Immunity and Quiet Designs<br>Defensive Design and Designing for Off-Nominal Events<br>Designing For Testability<br>RECONFIGURABLE FPGA TECHNOLOGY                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

| 10.1<br>10.2<br>10.3<br><b>11</b><br>11.1                                                                                                              | Noise Immunity and Quiet Designs<br>Defensive Design and Designing for Off-Nominal Events<br>Designing For Testability<br><b>RECONFIGURABLE FPGA TECHNOLOGY</b><br>Configuration Memory                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |

| 10.1<br>10.2<br>10.3<br><b>11</b><br>11.1<br>11.2                                                                                                      | Noise Immunity and Quiet Designs<br>Defensive Design and Designing for Off-Nominal Events<br>Designing For Testability<br><b>RECONFIGURABLE FPGA TECHNOLOGY</b><br>Configuration Memory<br>Redundancy                                                                                                                                                                                                                                                                                                                    |                                                                                                                                              |

| 10.1<br>10.2<br>10.3<br><b>11</b><br>11.1                                                                                                              | Noise Immunity and Quiet Designs<br>Defensive Design and Designing for Off-Nominal Events<br>Designing For Testability<br><b>RECONFIGURABLE FPGA TECHNOLOGY</b><br>Configuration Memory                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                              |

| 10.1<br>10.2<br>10.3<br><b>11</b><br>11.1<br>11.2<br>11.3<br>11.4                                                                                      | Noise Immunity and Quiet Designs<br>Defensive Design and Designing for Off-Nominal Events<br>Designing For Testability<br><b>RECONFIGURABLE FPGA TECHNOLOGY</b><br>Configuration Memory<br>Redundancy<br>Embedded Functions                                                                                                                                                                                                                                                                                              |                                                                                                                                              |

| 10.1<br>10.2<br>10.3<br><b>11</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>APP</b>                                                                        | Noise Immunity and Quiet Designs<br>Defensive Design and Designing for Off-Nominal Events<br>Designing For Testability<br><b>RECONFIGURABLE FPGA TECHNOLOGY</b><br>Configuration Memory<br>Redundancy<br>Embedded Functions<br>IN-FLIGHT RECONFIGURATION                                                                                                                                                                                                                                                                 | 35<br>35<br>36<br>37<br>37<br>37<br>37<br>38<br>38<br>38<br>40                                                                               |

| 10.1<br>10.2<br>10.3<br><b>11</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>APP</b><br><b>APP</b>                                                          | Noise Immunity and Quiet Designs<br>Defensive Design and Designing for Off-Nominal Events<br>Designing For Testability<br><b>RECONFIGURABLE FPGA TECHNOLOGY</b><br>Configuration Memory<br>Redundancy<br>Embedded Functions<br>In-flight Reconfiguration<br><b>ENDIX A – DEFINITIONS</b>                                                                                                                                                                                                                                 | 35<br>36<br>36<br>37<br>37<br>37<br>37<br>38<br>38<br>38<br>40<br>41                                                                         |

| 10.1<br>10.2<br>10.3<br><b>11</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>APP</b><br><b>APP</b>                                                          | NOISE IMMUNITY AND QUIET DESIGNS<br>DEFENSIVE DESIGN AND DESIGNING FOR OFF-NOMINAL EVENTS<br>DESIGNING FOR TESTABILITY<br><b>RECONFIGURABLE FPGA TECHNOLOGY</b><br>CONFIGURATION MEMORY<br>REDUNDANCY<br>EMBEDDED FUNCTIONS<br>IN-FLIGHT RECONFIGURATION<br>ENDIX A – DEFINITIONS<br>ENDIX B – ACRONYMS                                                                                                                                                                                                                  | 35<br>35<br>36<br>37<br>37<br>37<br>37<br>38<br>38<br>40<br>41<br>43                                                                         |

| 10.1<br>10.2<br>10.3<br><b>11</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>APP</b><br><b>APP</b><br><b>C</b> .1<br>C.2                                    | NOISE IMMUNITY AND QUIET DESIGNS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35<br>35<br>36<br>37<br>37<br>37<br>37<br>38<br>38<br>40<br>40<br>41<br>41<br>43<br>43                                                       |

| 10.1<br>10.2<br>10.3<br><b>11</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>APP</b><br><b>APP</b><br><b>APP</b><br>C.1<br>C.2<br>C.3                       | NOISE IMMUNITY AND QUIET DESIGNS<br>DEFENSIVE DESIGN AND DESIGNING FOR OFF-NOMINAL EVENTS<br>DESIGNING FOR TESTABILITY<br><b>RECONFIGURABLE FPGA TECHNOLOGY</b><br>CONFIGURATION MEMORY<br>REDUNDANCY<br>EMBEDDED FUNCTIONS<br>IN-FLIGHT RECONFIGURATION<br>ENDIX A – DEFINITIONS<br>ENDIX B – ACRONYMS<br>ENDIX C – SPECIAL PINS<br>ACTEL RTAX<br>ACTEL RTAX<br>ACTEL SX<br>XILINX 5VQV                                                                                                                                 |                                                                                                                                              |

| 10.1<br>10.2<br>10.3<br><b>11</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>APP</b><br><b>APP</b><br><b>APP</b><br>C.1<br>C.2<br>C.3                       | NOISE IMMUNITY AND QUIET DESIGNS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                              |

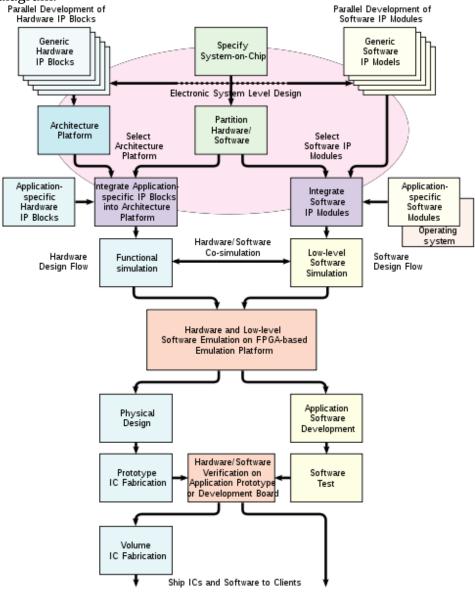

| 10.1<br>10.2<br>10.3<br><b>11</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>APP</b><br><b>APP</b><br>C.1<br>C.2<br>C.3<br><b>APP</b><br>D.1                | Noise Immunity and Quiet Designs<br>Defensive Design and Designing for Off-Nominal Events<br>Designing For Testability<br><b>RECONFIGURABLE FPGA TECHNOLOGY</b><br>Configuration Memory<br>Redundancy<br>Embedded Functions<br>In-flight Reconfiguration<br><b>ENDIX A – DEFINITIONS</b><br><b>ENDIX B – ACRONYMS</b><br><b>ENDIX B – ACRONYMS</b><br><b>ENDIX C – SPECIAL PINS</b><br>Actel RTAX<br>Actel RTAX<br>Actel SX<br>XILINX 5VQV<br><b>ENDIX D – SYSTEM ON CHIP (SOC) FPGA DESIGN PRACTICES</b><br>Design FLow | 35<br>36<br>37<br>37<br>37<br>37<br>38<br>38<br>40<br>40<br>41<br>41<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43                   |

| 10.1<br>10.2<br>10.3<br><b>11</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>APP</b><br><b>APP</b><br><b>C</b> .1<br>C.2<br>C.3<br><b>APP</b><br>D.1<br>D.2 | Noise Immunity and Quiet Designs<br>Defensive Design and Designing for Off-Nominal Events<br>Designing For Testability<br><b>RECONFIGURABLE FPGA TECHNOLOGY</b><br>Configuration Memory<br>Redundancy<br>Embedded Functions<br>In-flight Reconfiguration<br>ENDIX A – DEFINITIONS<br>ENDIX B – ACRONYMS<br>ENDIX C – SPECIAL PINS<br>Actel RTAX<br>Actel SX<br>XiLINX 5VQV<br>ENDIX D – SYSTEM ON CHIP (SOC) FPGA DESIGN PRACTICES<br>DESIGN FLOW<br>CODE REUSE                                                          | 35<br>36<br>37<br>37<br>37<br>38<br>38<br>40<br>40<br>41<br>41<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>44<br>44<br>44<br>45<br>45 |

| 10.1<br>10.2<br>10.3<br><b>11</b><br>11.1<br>11.2<br>11.3<br>11.4<br><b>APP</b><br><b>APP</b><br>C.1<br>C.2<br>C.3<br><b>APP</b><br>D.1                | Noise Immunity and Quiet Designs<br>Defensive Design and Designing for Off-Nominal Events<br>Designing For Testability<br><b>RECONFIGURABLE FPGA TECHNOLOGY</b><br>Configuration Memory<br>Redundancy<br>Embedded Functions<br>In-flight Reconfiguration<br><b>ENDIX A – DEFINITIONS</b><br><b>ENDIX B – ACRONYMS</b><br><b>ENDIX B – ACRONYMS</b><br><b>ENDIX C – SPECIAL PINS</b><br>Actel RTAX<br>Actel RTAX<br>Actel SX<br>XILINX 5VQV<br><b>ENDIX D – SYSTEM ON CHIP (SOC) FPGA DESIGN PRACTICES</b><br>Design FLow |                                                                                                                                              |

#### CHECK THE GSFC DIRECTIVES MANAGEMENT SYSTEM AT

http://gdms.gsfc.nasa.gov to verify that this is the correct version prior to use.

| APPE | ENDIX E – REVIEW OF FIELD PROGRAMMABLE GATE ARRAYS         |    |

|------|------------------------------------------------------------|----|

| E.1  | INTRODUCTION                                               |    |

| E.2  | USE THE CORRECT FPGA DATA SHEETS                           |    |

| E.3  | COLLECT THE NECESSARY REVIEW FILES                         |    |

| E.4  | PERFORMING THE REVIEW                                      |    |

| E.5  | REVIEW THE POR AND RESET CIRCUITRY AND POWER-UP CONDITIONS |    |

| E.6  | REVIEW THE PLAN FOR FUNCTIONAL VERIFICATION                | 55 |

| E.7  | REFERENCES, NOTES, AND RELATED DOCUMENTS                   | 55 |

| APPE | ENDIX F – REFERENCES                                       |    |

| F.1  | SPECIAL PINS                                               |    |

| F.2  | INPUT/OUTPUT (I/O)                                         |    |

| F.3  | CLOCKS                                                     |    |

| F.4  | FINITE STATE MACHINES                                      |    |

| F.5  | RESETS                                                     |    |

| F.6  | HAZARD ANALYSIS                                            |    |

| F.7  | POWER                                                      |    |

| F.8  | INTERFACING TO NON-VOLATILE MEMORIES (EEPROM, FLASH, ETC)  |    |

| F.9  | TIMING ANALYSIS                                            |    |

| F.10 | MISCELLANEOUS DESIGN GUIDELINES AND CRITERIA               |    |

| F.11 | RECONFIGURABLE FPGA TECHNOLOGY                             |    |

| APPE | ENDIX G – FPGA DESIGN CYCLE CHECKLIST FOR DESIGNERS        | 65 |

| CHAI | NGE HISTORY LOG                                            |    |

| DIRECTIVE NO.    | 500-PG-8700.2.7B |

|------------------|------------------|

| EFFECTIVE DATE:  | August 13, 2012  |

| EXPIRATION DATE: | March 30, 2021   |

#### PREFACE

#### P.1 PURPOSE

The purpose of this document is to discuss guidelines and criteria that form a basis for the design and evaluation of Field Programmable Gate Arrays (FPGAs) for high-reliability space-flight applications.

#### P.2 APPLICABILITY

This document is applicable to the development of all Goddard Space Flight Center FPGAs intended for high-reliability space-flight applications, as per GPR 8700.2, Design Development.

#### P.3 AUTHORITY

GPR 8700.2, Design Development

#### P.4 REFERENCES

500-PG-8700.2.8, Field Programmable Gate Array (FPGA) Development Methodology

#### P.5 CANCELLATION

500-PG-8700.2.7- Design of Space Flight Field Programmable Gate Arrays, Rev-

#### P.6 SAFETY

NONE

#### P.7 TRAINING

NONE

#### P.8 RECORDS

| Record Title                         | Record Custodian          | Retention                             |

|--------------------------------------|---------------------------|---------------------------------------|

| Design Verification Test and         | Product Design Lead (PDL) | * <u>NRRS 8/103</u>                   |

| Analysis<br>Reports and/or Summaries |                           | Engineering test and evaluation data. |

|                                      |                           | Temporary. Destroy                    |

|                                      |                           | between 5 and 30 years                |

|                                      |                           | after program/project                 |

|                                      |                           | termination.                          |

CHECK THE GSFC DIRECTIVES MANAGEMENT SYSTEM AT <u>http://gdms.gsfc.nasa.gov</u> to verify that this is the correct version prior to use.

\*NRRS- NASA Records Retention Schedules (NPR 1441.1 }

### P.9 MEASUREMENT/VERIFICATION

NONE

### PROCEDURES

In this document, a requirement is identified by "shall," a good practice by "should," permission by "may" or "can," expectation by "will," and descriptive material by "is."

### **INTRODUCTION**

As space vehicle missions have become increasingly complex, the use of onboard digital computers and high-density programmable logic has become more prevalent. The functions that the avionics are assigned to perform are also expanding in number and magnitude. As a result, specifying and designing digital avionics for space vehicles has increased in complexity.

The flight performance of spaceborne digital avionics has generally, but not always, been successful. A number of recurring problems have been experienced during the design, development, and testing of these machines. Failure to develop and adhere to proven practices and processes has resulted in costly redesigns that have caused significant schedule delays or, if fixes are not implemented, caused the project to accept a higher level of risk. Most difficulties have resulted from:

- a. Lack of established or proven design/analysis practices

- b. Incomplete knowledge of the newer technologies and tools coupled with their impact on the design and analysis

- c. Inadequate reviews

This document concentrates on items that have caused problems in space flight digital hardware, particularly FPGAs. This information does not provide guidance on how to design or code a particular circuit or how to perform analyses, but instead outlines recommendations that should be considered for a successful and robust design.

This document shall be used as a design resource to supplement other available formal manufacturer's resources including, but not limited to, datasheets, application notes, and errata for the selected FPGA device. Understanding and complying with the appropriate manufacturer's information is vital to a successful FPGA design. Although this document cites specific FPGA examples, it is the responsibility of the designer to confirm these recommendations in this document with the latest manufacturer's information before any implementation.

Although this document is not in a checklist format, a sample checklist is provided in Appendix G - FPGA Design Cycle Checklist for Designers. This checklist mirrors the recommendations found in this document. It is recommended that the checklist found in the appendix be used as a design aid throughout the design process. A filled in checklist can also be specified as a deliverable for design reviews.

In addition to what is textually included in this document, each of the following sections includes one or more links to additional, web-based material in the form of case studies, application notes, papers, and other material and references.

### **1** Special Pins

This section contains general information on special pins for all FPGAs. However, specific information on commonly used FPGAs can be found in Appendix F.1 – Special Pins

### 1.1 CONFIGURATION PINS: TERMINATE CONFIGURATION PINS PROPERLY

**Rationale**: A common problem identified during design reviews is the improper termination of special pins. For every device, carefully review data sheets and design schematics to confirm that each special pin is properly terminated. Termination of many of these special pins cannot be verified by test.

Ensure that each configuration pin is carefully checked against the latest data sheet. Some pins have very high internal pull-up resistors which can be compromised by highspeed signals on the board level. Also, some configuration pins can naturally just happen to float to the desired state with nominal operation observed. Beware of special pins such as programming pins that are required to be terminated appropriately for flight. A rule of thumb is to design defensively and ensure that intended signal levels are solid.

Different devices will have different pins and there is no overarching, general rule, other than to check each pin.

### 1.2 UNUSED INPUTS: DO NOT LEAVE UNUSED INPUTS FLOATING

**Rationale:** In general, all devices should have properly terminated inputs. For normal Complimentary Metal-Oxide Semiconductor, CMOS, devices, this is a requirement. Certain programmable devices such as FPGAs will often take care of unused pins via software, exploiting the programmable nature of the microcircuit. However, the "fine print" for each pin should be read carefully. For example, in Actel SX and SX-S, clock inputs such as HCLK or the global routed clocks do not have an output stage -- they are special purpose -- and thus have to be terminated by the user. Failure to do so can result in large unintended currents that could cause device damage.

| <b>EFFECTIVE DATE:</b> August 13, 2012 | Page 8 d |

|----------------------------------------|----------|

|                                        |          |

| EXPIRATION DATE: March 30, 2021        |          |

Depending on the device, pins labeled as "N/C" may be reserved by the manufacturer for internal purposes and terminating them on the board may result in problems. Conversely, not terminating N/C's in certain cases can be bad. Check each pin carefully according to the specification and clarify with the manufacturer if necessary.

### **1.3 TEST INTERFACE: FOLLOW MANUFACTURER'S RECOMMENDATIONS**

**Rationale**: Many devices have custom test interfaces that will have to be handled on a caseby-case basis. Since they hook up to test equipment, care should be taken in following the manufacturer's instructions. For example, Actel SX-S device test pins should be series terminated.

### 1.4 DEBUG INTERFACE: DISABLE FOR FLIGHT CONFIGURATION

**Rationale**: If FPGA input/output, I/O, are used to implement a debug interface for development, make sure that the inputs are safely jumpered or driven and that outputs are not toggling in the final flight configuration, causing unnecessary Electro-Magnetic Interference, EMI, and noise.

### 2 INPUT/OUTPUT (I/O)

This section looks at the various aspects of device I/O that a designer should consider.

# 2.1 SIMULTANEOUS SWITCHING OUTPUTS (SSOS): ADHERE TO THE VENDOR'S RECOMMENDATIONS FOR HANDLING SSO

**Rationale:** There may be limits to the number of output pins that can switch at one time. Sometimes these limits are specified by the manufacturer in a data sheet, described in an application note, and/or left to the discretion of the designer. With devices that switch faster and with large pin counts and lower Alternating Current, AC, and Direct Current, DC, noise margins, Ground/V<sub>DD</sub> bounce can be a serious issue which can dynamically affect input switching thresholds, decreasing system noise margins. It is also important to note that for many devices,  $t_{PD}$  can be negatively affected by the number of SSOs.

Care and planning is also important for pin assignments. Pin assignments that "look pretty" with all the data bits on a bus lined up in a row have been notorious for causing both ground bounce problems on the printed circuit card and routing problems inside FPGAs. Power integrity tools should be considered as they provide a means to accurately predict the effects of SSOs on a given design. Note the considerations below for simultaneous switching outputs and noise immunity and quiet designs.

Consider the following guidelines to minimize "bounce" issues.

- a. Use the lowest possible I/O slew rate and drive strength the design timing will support.

- b. Don't group SSOs together; break them up. Refer to the device datasheet for recommendations on allowable SSO signaling per ground pin.

- c. Control number of SSOs through sequencing. Example: Do address or data bus bits all need to switch at the same time?

- d. For some families, programming "unused" outputs will improve internal grounding or supply for output stages if terminated to the rail on the printed circuit board.

- e. When FPGA output drive is not sufficient, particularly for large memory arrays or long lines, use external buffers, being careful to adhere to proper PWB design techniques.

- f. Use sockets with caution. Do not use sockets for Flight applications.

- g. Choose input thresholds wisely.

- 1. Transistor-Transistor Logic, TTL,  $V_{IL} = 0.8V$  very sensitive. Try to avoid this setting, as it is sensitive to both ground bounce and ringing.

- 2. Try to choose input voltage threshold options, such as programmable 5V CMOS, that mitigates the effects of ground bounce

- h. Keep clocks physically away from pins that can cause ground bounce (i.e., high frequency switching pins, pins with high rise time, and address/data busses).

- i. Assign clocks to pins that are close to ground pins.

- j. Driving test data through the Joint Test Action Group, JTAG, test interface, especially over multiple parts can induce data pattern sensitivities, particularly with large data busses. For example, switching patterns from FFFFFFF to 00000000. Though this may be an artificial failure or an artifact of the test, this can damage or potentially overstress hardware through a loss of control.

- k. Test cabling, particularly for vibration, thermal/vacuum, and EMI tests will present different conditions for normal bench testing or systems application. Design for the worst- case over the entire project flow.

l. If applicable, consider the use of lower voltage I/O standards. FPGAs often have lower voltage I/O standards available. Lower voltage I/O have lower transient currents which can reduce SSO.

# 2.2 SIGNAL TERMINATION: ENSURE THAT OUTPUT SIGNALS ARE TERMINATED PROPERLY

**Rationale**: Start by using termination resistor values equal to the trace impedance minus the output impedance of the driver ( $R_{term} = Z_{trace} - Z_{driver}$ ) then perform signal integrity analysis to optimize the termination resistor values.

- a. Address edge sensitive signals, such as Clock output signals, with special care to ensure that there is a smooth transition through the threshold. For loaded clocks, perhaps traveling over long runs, reflections may often result in non-monotonic transitions causing false or double clocking. Note that this may happen on the "inactive" edge. Similarly, overshoot and ringing can also cause false clocking, particularly on the transition to ground. Unterminated nets could result in ringing which is a source of EMI even when it doesn't contribute to logic failures.

- b. Most manufacturers have tight limits on how far outside the rail a signal may travel, sometimes coupled with maximum time outside of the recommended limits. Ensure good signal quality as damage to I/O's may happen.

- c. Do plan on termination resistors in advance to support signal integrity analysis efforts. The signal integrity analysis may show that they can be eliminated. However, if they are required, adding them later could require additional time in layout, debugging, rework, and/or costly printed wiring board (PWB) respin.

- d. Review schematics for proper terminations on interfaces such as the Peripheral Component Interconnect, PCI, interface.

# 2.3 TRI-STATE BUS CONSIDERATIONS: AVOID CONTENTION AND FLOATING **Rationale:** Bus contention wastes power, needlessly generates noise, and stresses components.

a. Avoid contention when actively driving tri-state busses. Have a guaranteed off-time between drivers on the bus in the worst-case. A clock cycle between tri-stating one driver and enabling another may be sufficient but a thorough timing analysis is necessary. Be sure to consider timing parameters, which need to be added together. For example, the tri-state time of an external SRAM's OE (Output Enable) that is

controlled by an FPGA's state machine would be the sum of the Tco ("clock-to-out" delay) out of the FPGA + the travel time on the board + the SRAM's tri-state time.

- b. Do not allow the bus to float for a long time or have slow transition times, as this will increase power and noise and may negatively affect reliability.

- c. Consider parking the bus when not in use (drive to 1's or 0's) instead of using pull-up/ down resistors. Some FPGA's have a "keeper" I/O standard which does this.

- d. When parking a bus and still using pull-up/down resistors ensure that the bus is fully driven to the parked state before it is tri-stated to avoid ringing.

- e. For portability, infer a tri-state buffer in Register Transfer Level, RTL, code instead of instantiating a device-specific tri-state buffer.

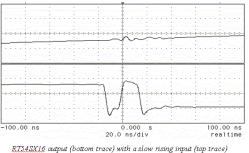

### 2.4 INPUT TRANSITION TIMES: EXAMINE INPUT SLEW RATE

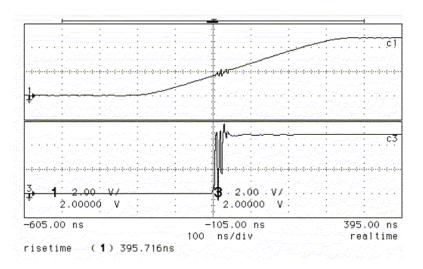

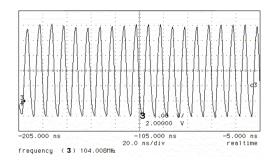

**Rationale:** Some high-speed devices have very stringent restrictions on input transition times, often being surprisingly tight. Failure to meet the requirements may result in oscillations (Figure 2-1), multiple clocking, or damage.

Figure 2-1 – Glitches Due To Input Slew Rate Violations

Simple pull-up or pull-down resistors, with transition times in the hundreds of nanoseconds, may be too slow. Take appropriate precautions if older digital logic families are used which may have outputs that are not compatible (e.g. too slow) with high-speed devices

### 2.5 SHORTING OUTPUTS TOGETHER: AVOID SHORTING OUTPUTS TOGETHER

**Rationale**: This is sometimes done to increase drive on the board. This should be avoided since it may damage components if the switching speeds are not matched and it can be

| DIRECTIVE NO.    | 500-PG-8700.2.7B | Page 12 of 102 |

|------------------|------------------|----------------|

| EFFECTIVE DATE:  | August 13, 2012  |                |

| EXPIRATION DATE: | March 30, 2021   |                |

difficult or impractical to test this redundant topology. If this needs to be done, consider using an external buffer or splitting the loads between 2 or more nets, each driven by a single output.

### 2.6 MIXED I/O STANDARDS: *EXAMINE VOLTAGE THRESHOLDS, DC COMPATIBILITY, AND NOISE MARGINS*

**Rationale:** When mixing devices from multiple families, even from the same manufacturer, Exercise extreme care to ensure that the devices are reliably operated and that there is sufficient noise margin. This may be problematic when substituting parts for either upgrading circuit performance or dealing with obsolescence issues.

For inputs, many CMOS technology devices advertise "TTL compatible" inputs. However, these inputs may in fact differ rather significantly from their TTL counterparts. The first major difference for many but not all devices is the impedance presented to the interface when power is removed from the device. For example, when radiation-hardened CMOS latches were substituted for soft 54LS373's in the Galileo attitude control computer's memory units, block redundancy circuits failed since the engineers didn't take into account the sneak path through the radiation-hardened inputs electrostatic discharge (ESD) protection diodes when power was removed. Another related difference is the maximum voltage that can be applied. Some bipolar devices are useful for reliable level shifting from higher voltages to lower ones; CMOS replacement devices will forward bias the protection diodes resulting in unintended current flows and possible damage or circuit failure. Lastly, many CMOS inputs have logic thresholds, which are not truly TTL compatible. That is, the TTL V<sub>IH</sub> specification is often not met, with V<sub>IH(max)</sub> values of 2.2V, 2.4V, and sometimes 2.5V being specified whereas true TTL devices have a threshold defined by two diode drops, typically in the range of 1.2V to 1.4V. TTL outputs are only guaranteed to drive to  $V_{OH} = 2.4V$ so there may be little or even negative noise margins present in these situations. The switching point difference can also lead to circuit failure, depending on the signal integrity. Often TTL outputs, when switching, have a "bump" in the waveform, particularly with heavy and/or long loads. While this "bump" is often at a high enough voltage so that TTL devices operate correctly, the often higher V<sub>IH</sub> of CMOS devices may result in multiple clocking. Pull-up resistors can restore adequate DC noise margins in these situations if given enough time to settle, which may be quite a while for this passive circuit. Note, however, that TTL to CMOS clock interfaces designed in this fashion will often fail logically since the CMOS input may see multiple transitions resulting in double clocking.

CMOS output stages can also be tricky and subtle device characteristics can cause errors. Check all specifications carefully! For example, many CMOS devices when driving loads are

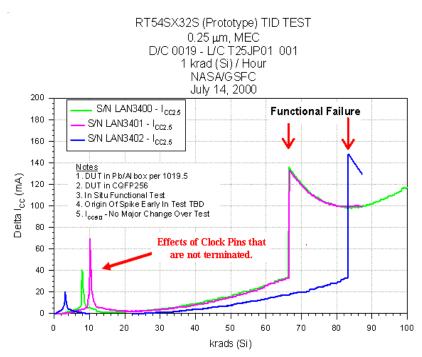

specified at only very low current levels for high or logic '1' signals. However, TTL inputs take substantial currents and do not present the high impedance seen by CMOS FET inputs and the output may be dragged down. For output loads that are a mix of CMOS and TTL inputs, split the loads to guarantee the high voltage needed for the CMOS inputs, typically 70% of  $V_{DD}$ , and the high current needed for TTL inputs, with the lower  $V_{IH}$  of 2.0V. Another factor to consider is the structure of the output stage in the CMOS device. For example, some devices will not swing all the way to the high rail and are voltage limited. This may result in some totem-pole current if the p-channel FET in the next input stage is not cut off. Some devices, even with a 5V I/O supply like the RT54SX series, will only drive outputs to the core voltage of 3.3V, making this CMOS output incompatible with 5V CMOS inputs on the same board! This was fixed in the 2.5V core RT54SXS series, with full 5V voltage swings when supplied with a 5V I/O bias.

Components today can typically have many supply voltages, including 1.5V, 1.8V, 2.5, 3.3V, and 5.0V. There are also an abundance of I/O standards with the newest devices being very programmable so their characteristics are not obvious or even known from a viewing a circuit schematic. Thus, carefully verify I/O compatibility, particularly when substituting "new and improved" devices or alternate devices.

### 2.7 POWER SWITCHING AND COLD SPARING: EXAMINE ALL CONFIGURATIONS

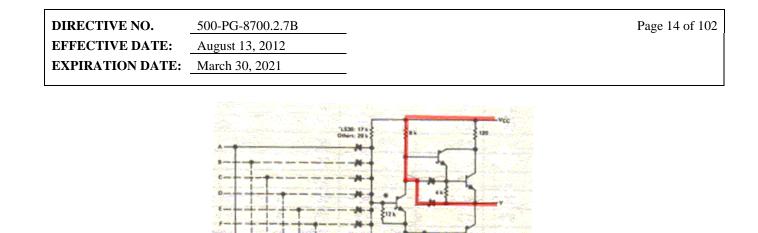

**Rationale:** A system designed with blocks that are independently powered should be analyzed in all different power switching configurations. Many CMOS devices present a low impedance when powered down through either the intrinsic or ESD protection diodes; others, with cold sparing inputs, may have high input impedance that is suitable for operation. For programmable devices, selecting 3.3V PCI compatibility, as one example, can result in a "cold sparing" device no longer being high impedance since a clamping diode will be enabled. While many bipolar devices are compatible with cold sparing architectures, some devices have a sneak path (Figure 2-2) to V<sub>CC</sub> through the output. Be sure to consider test setup not just the flight configuration. For example, does a piece of test equipment need to be powered up and down co- incident with the flight unit?

'LS00, 'LS04, 'LS10, 'LS20, 'LS30 CIRCUITS The 12-kΩ resistor is not on 'LS30.

Figure 2-2 – Sneak Path in Some LSTTL From Output to Vcc

| DIRECTIVE NO.           | 500-PG-8700.2.7B |

|-------------------------|------------------|

| EFFECTIVE DATE:         | August 13, 2012  |

| <b>EXPIRATION DATE:</b> | March 30, 2021   |

| EXPIRATION DATE:        | March 30, 2021   |

### 3 CLOCKS

Clocking, finite state machine design, and timing analysis are all intimately interrelated. This section will discuss some design criteria for clocks.

### 3.1 CLOCK BUFFERS: USE LOW SKEW CLOCK BUFFERS ON CLOCK AND RESET NETS WHERE POSSIBLE

**Rationale:** Low skew clock buffers simplify timing analysis, allow higher clock frequencies, and are less susceptible to SET events. In general, when designers use routed clock resources, the chip may more or less "work" with perhaps some unexplained glitches or a poor "programming yield" that is susceptible to specific routing. So, when sequentially adjacent flip-flops are clocked on a common edge, ensure that low-skew clock resources are used. It is acceptable to design with routed clocks and this can often result in a reduction of power or an effective increase in the number of clocks available. However, ensure that careful skew-tolerant design techniques and analyses are employed. Also, routing clock signals over long distances inside the FPGA makes it vulnerable to crosstalk from nearby aggressors. This can result in unpredictable behavior. Ensure that FPGA clock pin is close to clock buffer input.

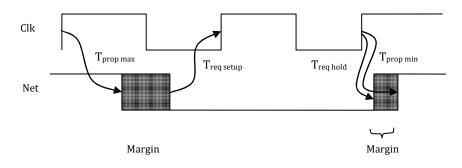

### 3.2 CHIP-TO-CHIP TIMING STRATEGY: PERFORM BOARD LEVEL TIMING ANALYSIS

**Rationale:** Many analysis tools are good at analyzing logic within a single chip. However, many are ineffective at analyzing system or chip-to-chip timing. It is tempting to simply use a low-skew clock on a board to hook up various digital devices. However, that is not always guaranteed to work so employ proper timing analysis to address setup and hold time. This is often overlooked or done improperly. While the worst-case behavior of the clock-to-out of the source chip is easily analyzed using "minimum" or "best case" timing parameters, analyze the hold time of the sink chip assuming a slow path for the clock and a fast path for the data, for the same calculation. Automated tools often do all min or all max but are not capable of doing a mixed analysis; often requiring a human to perform this task. A good goal for the sink chip is to have a hold time of 0 ns or less (negative hold) but many devices, particularly some models of FPGA, do not satisfy this condition. So, alternate techniques for passing signals should be used, such as opposite edge clocking, treating signals as asynchronous, etc. The criteria for passing is that all worst-case setup and hold times are always satisfied or that sufficient metastable state protection is included.

# 3.3 DELAY LOCK LOOPS, DLLS, AND PHASE LOCK LOOPS, PLLS: CONSIDER THE AMOUNT OF ANALYSIS REQUIRED BEFORE USING THE DLLS AND PLLS

| DIRECTIVE NO.           | 500-PG-8700.2.7B |

|-------------------------|------------------|

|                         | August 13, 2012  |

|                         | ,                |

| <b>EXPIRATION DATE:</b> | March 30, 2021   |

**Rationale:** DLLs and PLLs can have many useful functions in digital systems. However, understand and address all design considerations. First check that the worst-case frequencies (both slowest and fastest) are compatible with the circuits; often the acceptable ranges are very limited. Additionally, there are often signal quality conditions that need to be satisfied. Next, when these circuits clock finite state machines or other sequential logic, note the time to lock and stabilize for these circuits and ensure that the device and system powers up safely. Another item to check is the worst-case performance when the DLL or PLL is hit by an SEU. This can result in a change of programming of the DLL or PLL, which is sometimes a little subtle, or a change in mode. Ensure safe operation of the system occurs during these off-nominal conditions. Furthermore, an SEU or SET can cause the DLL or PLL to unlock or glitch and consequently make the entire circuit that is within the clock tree become chaotic (unstable) or inoperable, necessitating a reset.

Use of internal DLL/PLL FPGA circuitry should not even be considered without careful analysis of the program's radiation requirements and radiation test data on the FPGA's DLL/PLL circuitry.

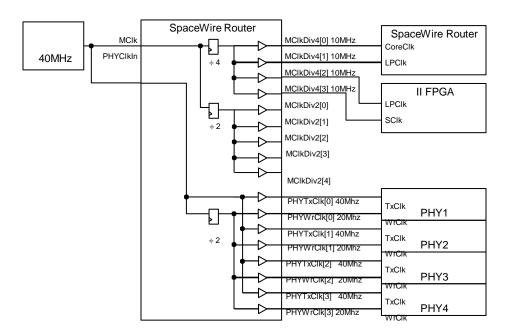

### 3.4 CLOCK TREE DIAGRAM: DRAWA BOARD LEVEL CLOCK TREE DIAGRAM

**Rationale:** A diagram should be drawn showing the clock trees for the circuit. These diagrams should include PLLs, DLLs, clock buffers, clock dividers, and all chips that use the clock. See Figure 3-1 below as an example.

### Figure 3-1 – Sample Clock Tree Diagram

### 3.5 CROSSING CLOCK DOMAINS: PERFORM CLOCK DOMAIN CROSSING ANALYSIS

**Rationale:** Based on analysis of the clock trees, identify all blocks and signals crossing clock domains and determine the need for metastable state resolution. Additionally, ensure that the latency involved in signal synchronization is tolerable to the system. Note that synthesis and place and route tools can help with this analysis.

### 3.6 FLIP-FLOP REPLICATION: AVOID UNINTENDED FLIP-FLOP REPLICATION

**Rationale:** Flip flop replication should be avoided in re-synchronizers because one part of the re- synchronizer will regularly disagree with another due to meta-stability and routing delay differences. This is likely to cause unpredictable behavior.

### 3.7 OPPOSITE EDGE CLOCKING: CONSIDER DUTY CYCLE IN TIMING ANALYSIS FOR DESIGNS THAT USE BOTH CLOCK EDGES

**Rationale:** For designs passing data from one edge of a clock to the other, ensure that the worstcase duty cycle for each phase is properly computed. Often designers will assume a 50% duty cycle which is not the case. Sources of duty cycle distortion include oscillator characteristics where duty cycle variation can be as much as +/- 10% and uneven delays through logic gates and buffers. If opposite edge clocking is not required consider avoiding this technique as it complicates the timing analysis for the design.

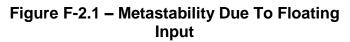

### 3.8 METASTABILITY: FILTERING TECHNIQUE SHOULD CONSIDER THE DURATION OF THE COMPONENT METASTABILITY

**Rationale:** Ensure that proper synchronizers are used for each asynchronous signal. Often designers will simply use two series D flip-flops. While an often used and acceptable topology, for very high-speed circuits for the technology in question, the failure rate of this synchronizer can be non-negligible. It may be necessary to add a third series D flip-flop. Also note the conditions for which the flip-flop's metastable parameters are taken, with large differences possible in resolution time when moving from nominal temperature and voltage to the extremes. Ensure that there is margin in these circuits as they are impractical to test and verify. Also note that for ASICs, different flip-flop macros may have significantly different metastable parameters. This can also be a consideration in FPGAs.

### 3.9 LATCHES : AVOID THE USE OF LATCHES

**Rationale**: Use of latches complicates the timing analysis of a design. Furthermore, place and route tools do not analyze timing paths with latches well. It is not uncommon that a latch can be replaced in a design dy and is flop and the second approach is to replace latches with flip more second to verify that this is the correct version prior to use. GSFC 3-18 (11/09)

| DIRECTIVE NO.           | 500-PG-8700.2.7B |

|-------------------------|------------------|

| EFFECTIVE DATE:         | August 13, 2012  |

| <b>EXPIRATION DATE:</b> | March 30, 2021   |

### 4 FINITE STATE MACHINES, FSM

What is the best style for a finite state machine? Should the human or the machine perform state assignment? How do we design safe finite state machines? There is no best answer for all situations and there is no magical style to be checked. It does, however, have to follow the basic principles of good logic design. It is noted that many engineers now use Hardware Description Languages, HDLs, to design the state machine and never see the logic. Extreme care is a requirement for critical applications. Finally there are very few designs with a single independent state machine. Most designs have several, if not many, interconnected state machines. Any correction algorithm would need to take into account all of the interconnected state machines and be thoroughly analyzed and tested in order to verify the proper operation. The correction method may even reside at a higher level such as at the subsystem card, or box level.

# 4.1 CRITICAL STATE MACHINES: ANALYZE ALL POSSIBLE STATE TRANSITIONS AND IMPLEMENT A DEFAULT STATE

Rationale: For critical state machines, the analysis should cover all possible logic states and demonstrate that the machine behaves in a deterministic and desired fashion. This includes consideration of off-nominal events. One credible failure mode example is an SEU. State machine analysis should include all physical states (all possible state vector values). It is a credible failure mode to be in any of these states as a result of a disturbance on the power bus, an ESD event, etc. Any high reliability machine is required to be robust under all credible failure modes. Additionally, verify that the FSM always starts in a legal state and then transitions through the desired sequences. One method is to use a power-on reset (POR) indicator. This should be checked to ensure that it is synchronous with the clock. One may not need any reset for a finite state machine if it can be shown to always go into a desired state. This can be done in the trivial case of a divide by n master counter, for example, where a reset is not needed and a fault on the reset line can halt the machine. Another technique is to gate the inputs with the POR signal and design an FSM such that it is guaranteed to go into a hold state. One consideration with the reset function is designfor-test and design-for-simulation, which sometimes results in additional reset connections.

# 4.2 STATE ENCODING: USE STATE VECTOR ENCODING SCHEME THAT MEETS REQUIREMENTS

Rationale: The choice of state vector encoding is one that should factor in radiation effects, timing

| DIRECTIVE NO.           | 500-PG-8700.2.7B | Page 19 of 102 |

|-------------------------|------------------|----------------|

| EFFECTIVE DATE:         | August 13, 2012  |                |

| <b>EXPIRATION DATE:</b> | March 30, 2021   |                |

constraints, and criticality of operation. Often, designers allow the synthesizer to choose the encoding scheme which is optimal for timing constraints; however the designer should review the synthesizer's choice factoring in radiation effects and criticality of operation. Here are some factors to consider.

- a. In FPGA where the flip-flops are inherently triplicated, upsets are more common from SETs than SEUs, thus, combinatorial logic poses a greater vulnerability. One-hot encoding uses more SEUs, but less combinatorial logic to encode the states and becomes a robust high- speed option.

- b. With one-hot encoding, all single bit errors are detectable, however, when one-hot encoded state machines experience an upset, it is likely that two state bits will become 'hot' and activate two parts of the design that aren't normally activated simultaneously. The designer should consider if this situation could cause any damage.

- c. With binary coded state machines, detecting illegal states and transitions requires the use of additional logic which increases susceptibility to radiation effects.

- d. It is tempting to think that if binary encoding is used and all 2<sup>n</sup> are defined that the FSM cannot lock up, however, this may not be the case if the FSM 'hand-shakes' with external logic. In this situation, an SEU could disrupt the normal sequence of operation and cause grid-lock.

- e. In the big picture, the difference in upset rates between state machine types is insignificant as they all show very low upset rates. Hence, a basic rule of thumb is to use one-hot encoding for speed and binary encoding for circuits with a large number of states.

# 4.3 HDL SYNTHESIZED MACHINES: ANALYZE THE SYNTHESIS REPORTS AND SYNTHESIZER OUTPUTS

**Rationale:** Obviously, all of the criteria for schematic-based machines apply. However, there are special considerations for designing with HDL, as the Computer-Aided Engineering, CAE, writer might generate circuits that are not desirable for high-reliable circuits. Hence, for critical circuits, examine the output reports from the synthesizer very carefully. Common things to check for include: recognized state machines; lockup states; outputs of Gray encoded machines that can glitch: unintended flip-flop replication; not implementing the desired and specified style (sometimes the synthesizers just think they know better than the human and will substitute one type of state machine for another). Additionally, some logic synthesizers will generate "safe" state machines. Use of this feature is not recommended because it typically increases the use of combinatorial logic which increases the SET susceptibility. If this feature is used, examine the generated design carefully. For CHECK THE GSFC DIRECTIVES MANAGEMENT SYSTEM AT

http://gdms.gsfc.nasa.gov to verify that this is the correct version prior to use.

| DIRECTIVE NO.          | 500-PG-8700.2.7B | Page 20 c |

|------------------------|------------------|-----------|

| <b>EFFECTIVE DATE:</b> | August 13, 2012  | _         |

| EXPIRATION DATE:       | March 30, 2021   | _         |

instance, it has been seen that sometimes the logic will explode with excessive gates. Other times there are resets generated on the opposite edge of the clock resulting in tight timing for the removal of clears which are not visible to the designer. Note that when using enumerated states in HDLs, not all physical states will be covered (only enumerated states are covered). Hence, the "others" clause will only refer to states in the enumerated type and not the physical realization. The HDL doesn't know if it is a one-hot or binary or gray coded implementation and what flip-flops have been replicated. This is not detectable at the black box simulation level nor by Boolean equations for logical equivalence.

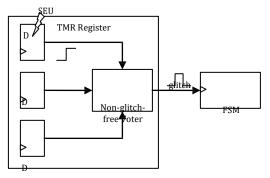

### 4.4 ERROR DETECTION AND CORRECTION, EDAC: ADDRESS FSM LOCKUP AT A HIGHER LEVEL AND ANALYZE FSM OUTPUTS

**Rationale**: It is often tempting to design robust state machines by simply appending a Hamming code and correction circuits. Hazard events are not synchronized to the system clock and the logic network is not guaranteed to be glitch free; do not rely on the ability of this type of structure to provide robust operation. In the general case, analyze the combinational circuits which implement the next-state logic and their inputs to the flipflops making up the state register. In particular, for any of these schemes, look at whether or not the circuit implementations are static hazard free (see Section 6) and, if not, can an erroneous transition to a state (or set of states) be made.

Heavy ion testing has proven that upsets in the EDAC logic will upset a state machine. Thus, EDAC protection for FSMs is not recommended.

In general, each FSM should be analyzed to make sure that the system can detect a locked up FSM and return it to a known state in a timely manner. This can be automated into the design or as simple as power cycling the box if acceptable to the system design. For mission critical applications, the FSM outputs should have external protection requiring FSW to 'arm' the FSM outputs.

| DIRECTIVE NO.           | 500-PG-8700.2.7B |

|-------------------------|------------------|

| EFFECTIVE DATE:         | August 13, 2012  |

| <b>EXPIRATION DATE:</b> | March 30, 2021   |

### 5 Reset

The term "reset" in this document refers to signals that drive asynchronous reset or preset inputs of clocked logic, typically flip-flops.

Synchronous resets can typically be analyzed with just static timing analysis as far as the FPGA is concerned but require board, box and/or system analysis to determine if indeterminate FPGA outputs are acceptable until the synchronous reset is clocked through.

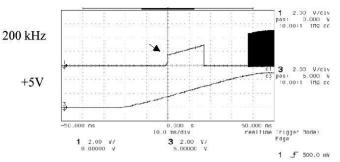

### 5.1 RESET LOGIC CIRCUIT (CONSIDER TRANSIENT BEHAVIOR): *PROVIDE SUFFICIENT NOISE MARGIN, ADEQUATE SLEW RATE, AND GLITCH FILTERING*

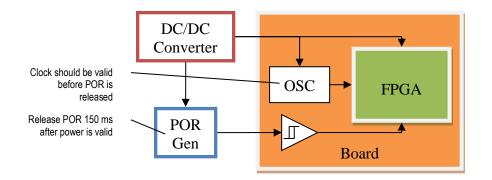

**Rationale:** Transient effects analysis are a major focus when analyzing reset circuitry performance. For the application of power, the output of the POR or reset circuit should ideally be a solid logic level and be glitch-free. This requires the POR circuitry to be designed using logic elements which operate correctly at the low ramping up voltages seen during power up. This insures that the POR signal is active at earliest time possible in the power-up-down sequence of events. Verify Inrush currents to timing capacitors do not exceed the maximum for that capacitor type. Verify rise times to logic gates, if used as a comparator, do not exceed the gate input's specifications; often gates with hysteresis inputs are used. Note that even with that type of input, output glitches may occur and several stages of logic gates may be required. The most robust solutions often utilize a comparator. Another transient factor to consider is the rise time of the flight power supply, both best and worst cases. These will often differ substantially from laboratory supplies and may be non-monotonic or have substantial overshoot and ringing. Note that flight power supplies are often slew-rate limited to minimize conducted emissions on the power bus. The time constant of the supply may exceed that of the POR circuit! For discharge, ensure that there is a low impedance path for timing capacitor discharge and that the inputs of logic gates are protected. Most CMOS inputs, but not all, have ESD diodes from the input to the supply rail. Discharging a large capacitance through that input may damage it. Also, consider the requirements and response of the circuit to momentary disruptions on the power bus. While many circuits may recover or be recoverable from a power-on reset, this is not true for all circuits. One such example is non-volatile, erasable memories, which need to be carefully protected.

Many diagrams of reset circuits show "asynchronous application, synchronous removal" of the reset circuit. However, note that for many devices, in particular many programmable devices, the inputs can be blocked or ignored during the power-on transient. This may be CHECK THE GSFC DIRECTIVES MANAGEMENT SYSTEM AT

http://gdms.gsfc.nasa.gov to verify that this is the correct version prior to use.

because of the need for charge pumps to start or configurations to be loaded and then released. For devices with synchronized inputs, clock oscillators are required to start, perhaps taking many tens of milliseconds, before the reset can be applied. This is a boardlevel consideration that is necessary to prevent the reset, which may look just fine on the schematic or in the HDL code, from being ignored by the real circuits. See Figure 5-1 below.

### Figure 5-1 – Recommended Power On Reset Implementation

Steady state or DC effects are also important. Check the leakage currents of timing capacitors and logic gates, as the amount of leakage current times the resistance of the timing resistor may result in a voltage drop that eliminates all noise margins.

### 5.2 RESETS: IMPLEMENT SYNCHRONOUSLY DE-ASSERTED RESET USING A GLOBAL BUFFER, IF AVAILABLE

**Rationale**: For asynchronous presets and clears, there are two basic parameters that need to be met. First, removing the preset or clear from a device asynchronously to the clock may result in meta-stable states in the sequential circuit. This parameter is frequently called the removal time and is denoted as t<sub>REM</sub>. Unfortunately, many data sheets do not specify the removal time. Use a synchronously de-asserted reset to ensure that the removal time requirement is met.

Second, if a global buffer is not available, the reset signal should be buffered to meet overall fan-out constraints. If this buffering takes too many resources, then the reset signal's fan-out constraint may be relaxed as long as timing is still met. Also, some flip flops may not need to be reset if their initial values don't matter.

### 5.3 RESET TREE: GENERATE RESET TREE DIAGRAM

CHECK THE GSFC DIRECTIVES MANAGEMENT SYSTEM AT <a href="http://gdms.gsfc.nasa.gov">http://gdms.gsfc.nasa.gov</a> TO VERIFY THAT THIS IS THE CORRECT VERSION PRIOR TO USE.

| EFFECTIVE DATE: August 13, 2012 | DIRECTIVE NO.           | 500-PG-8700.2.7B |